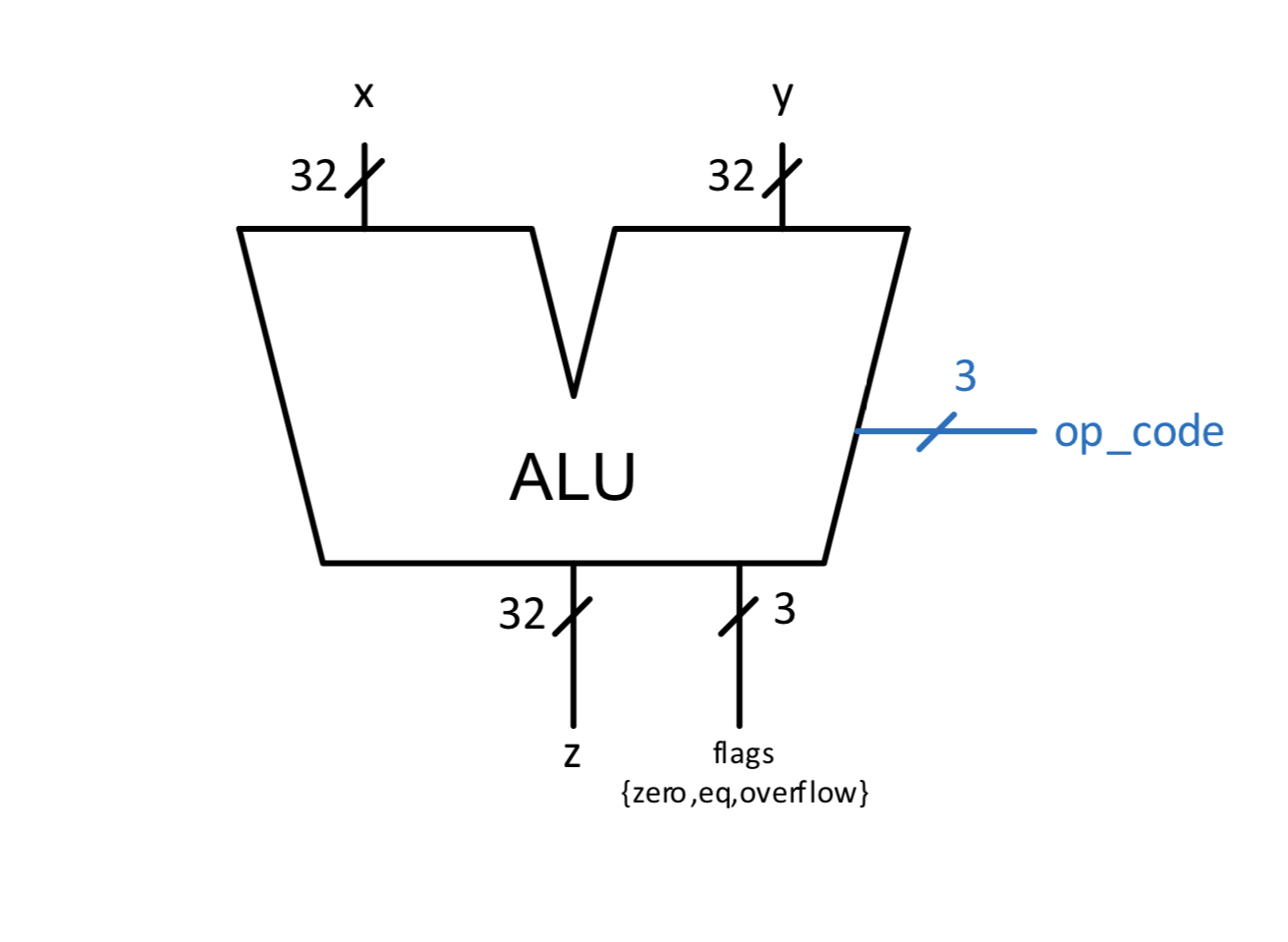

32-bit Arithemtic Logic Unit (ALU)

SystemVerilog

FPGA

Vivado

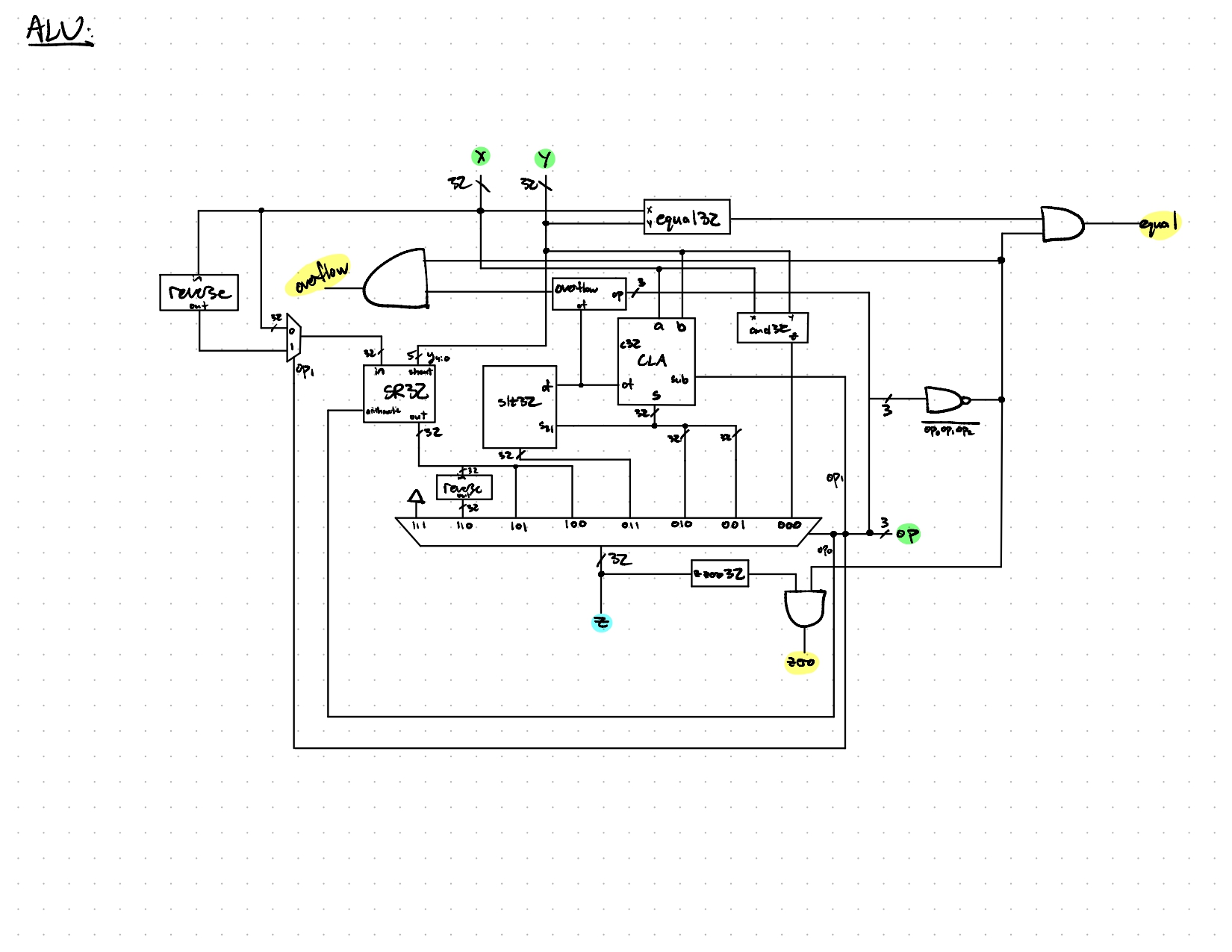

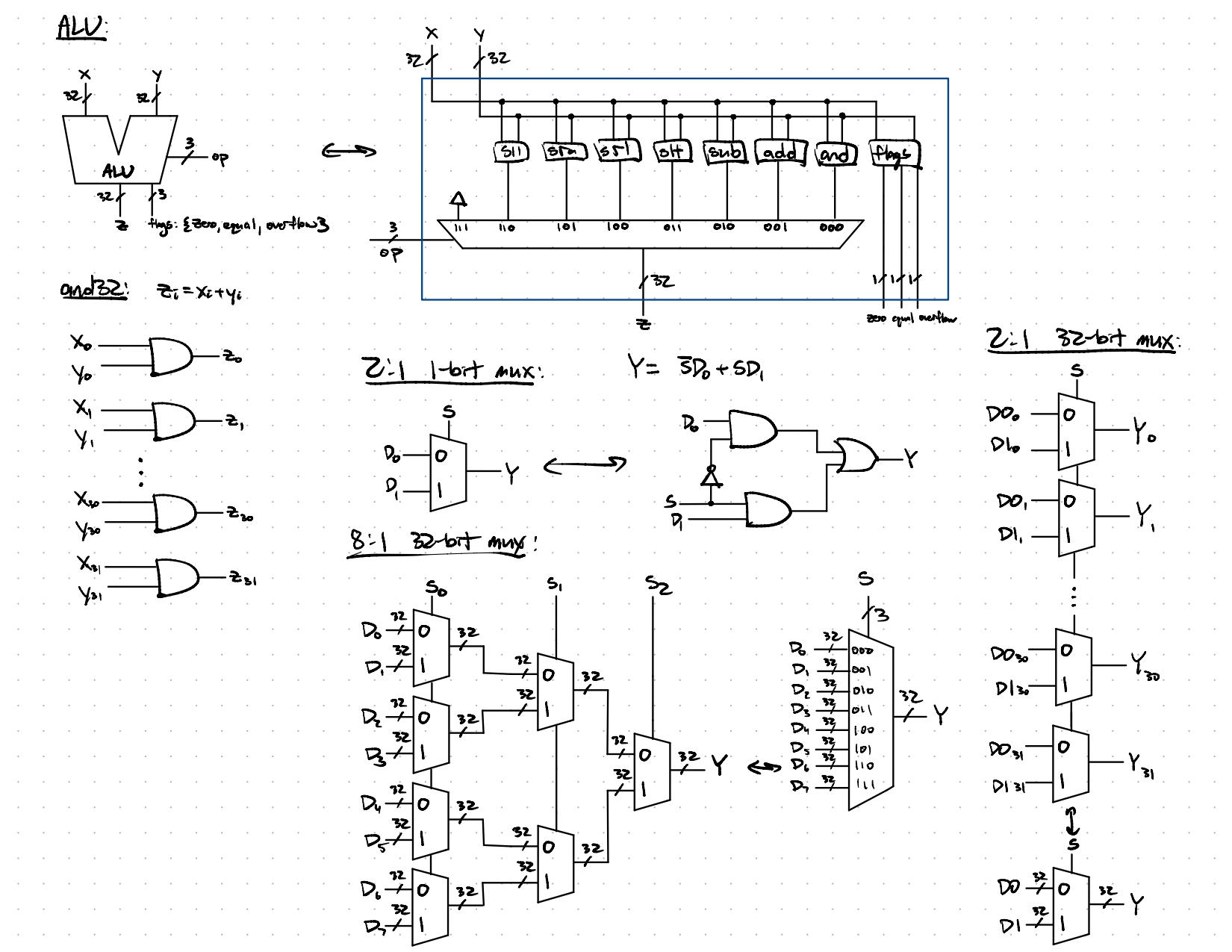

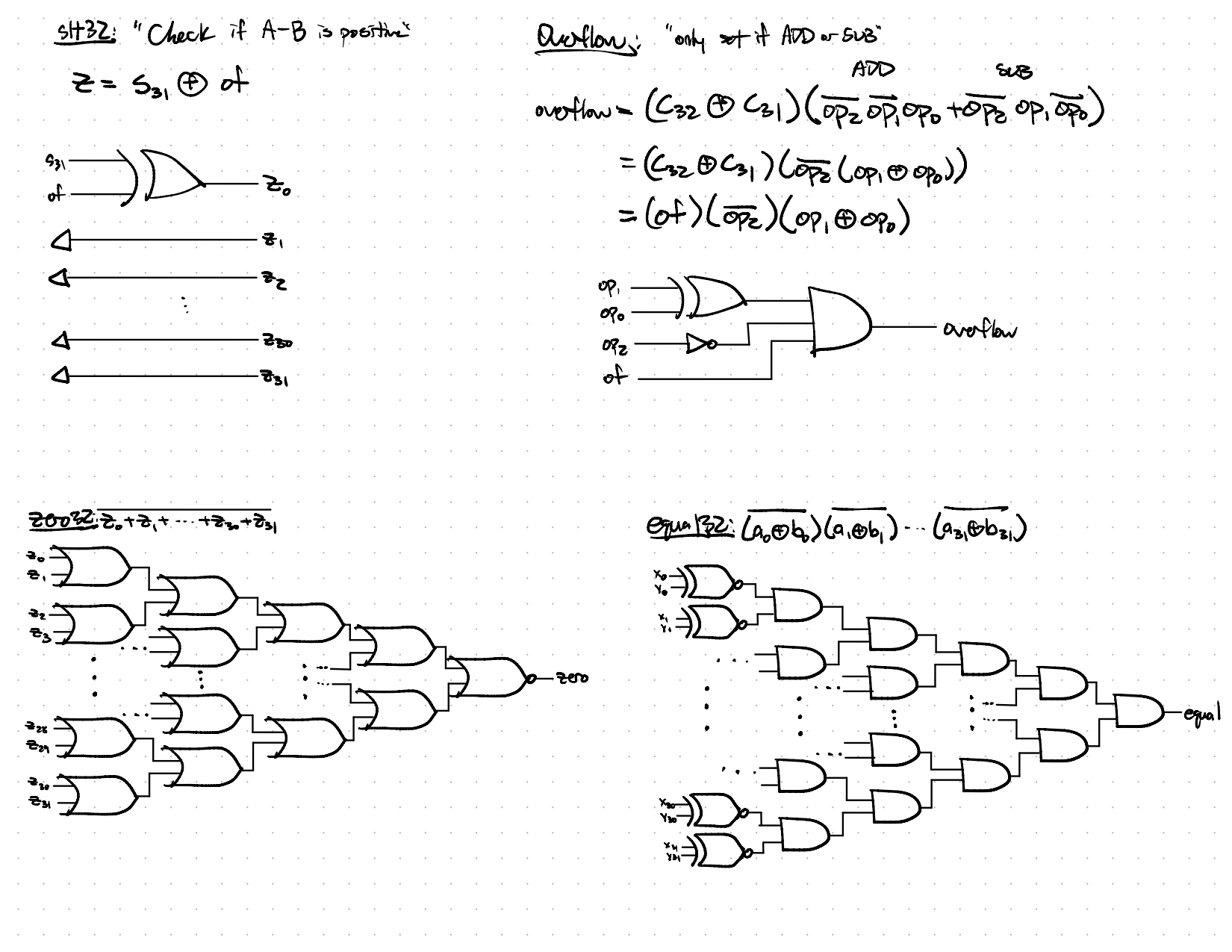

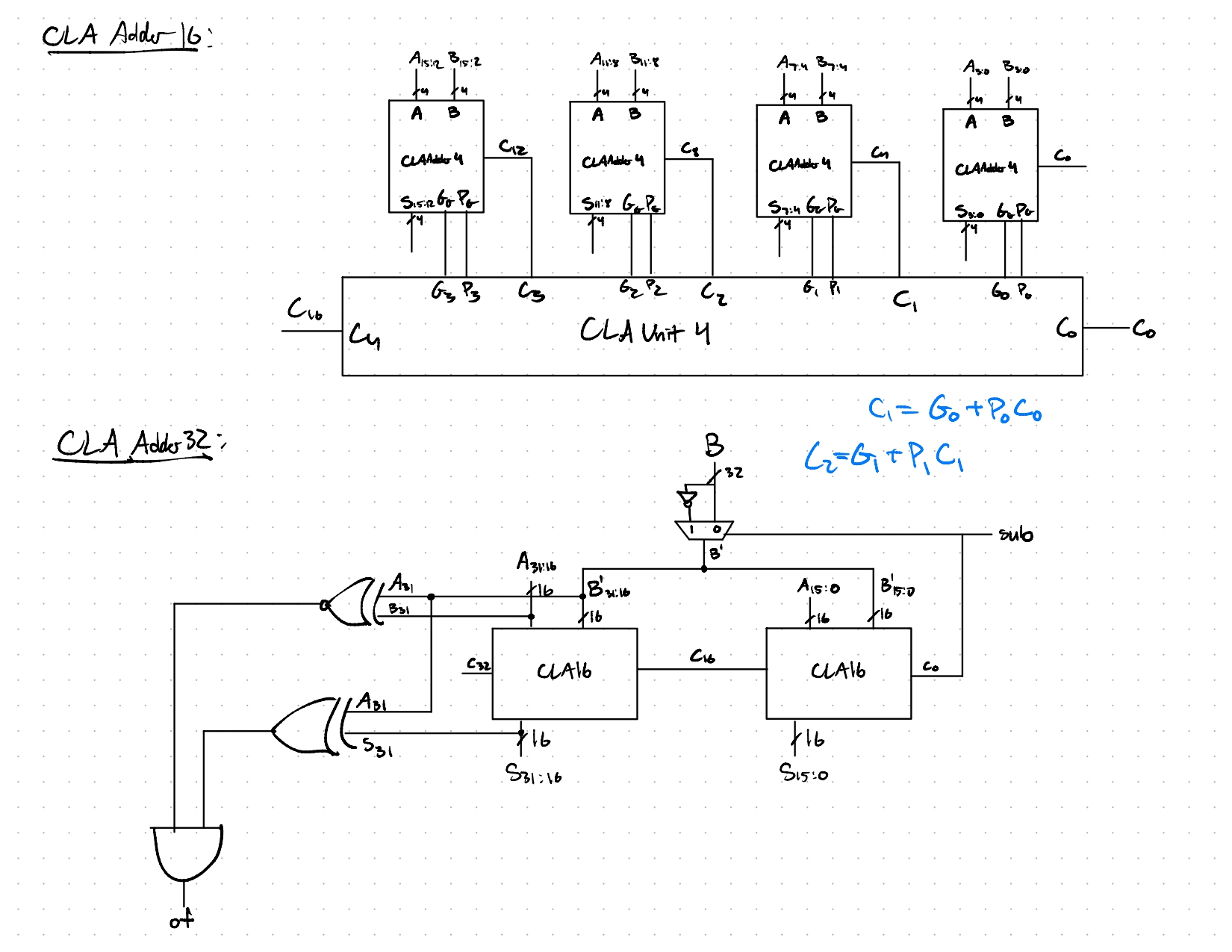

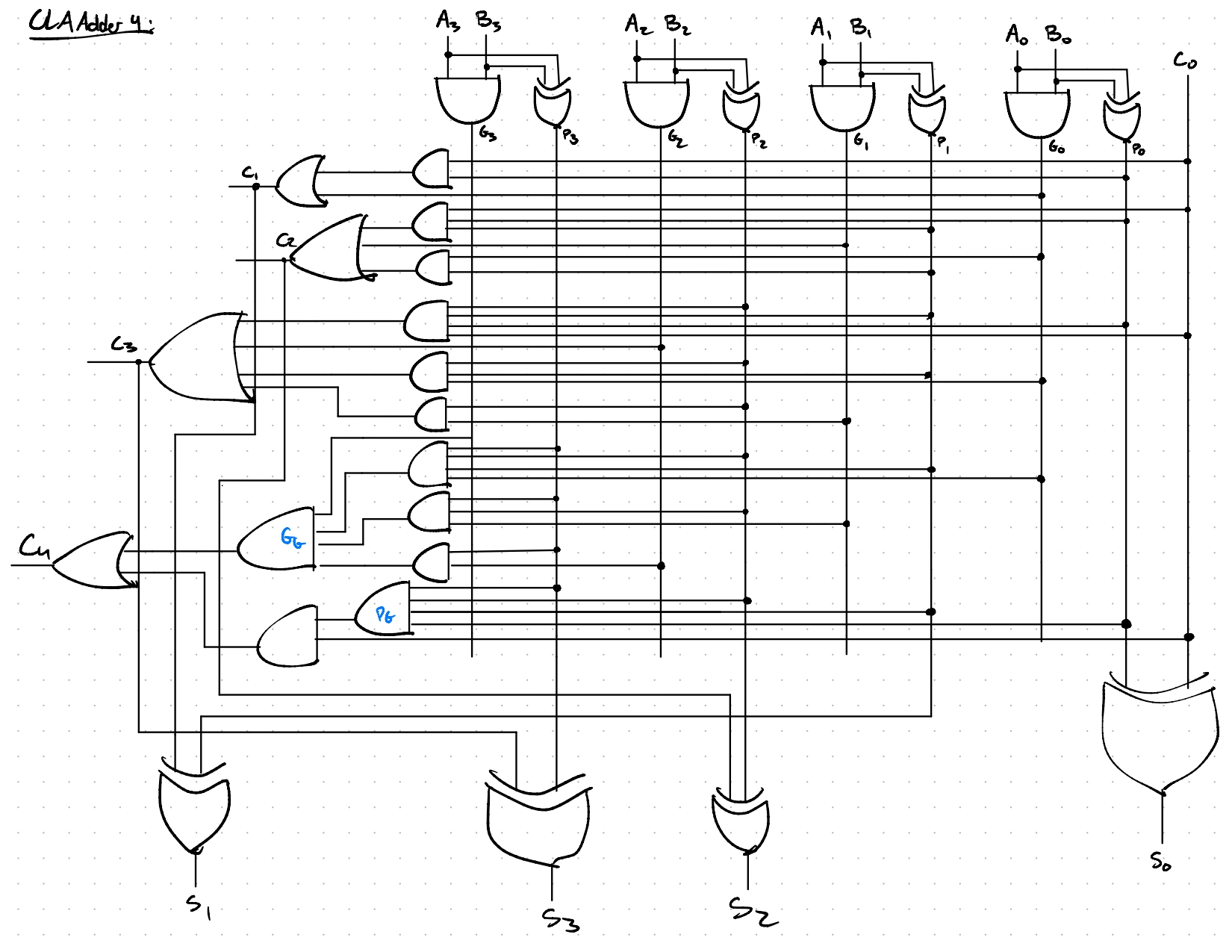

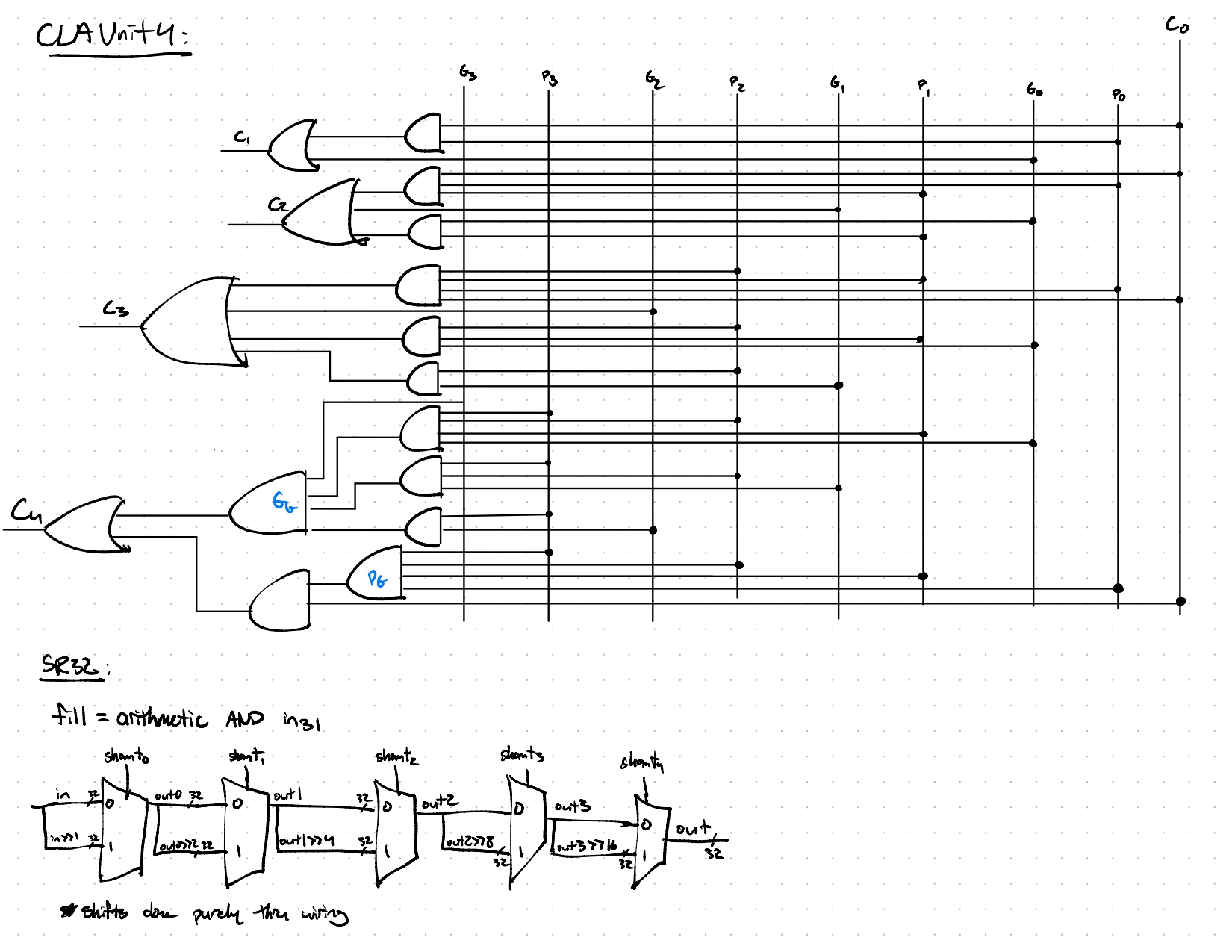

Created a 32-bit ALU with a carry-lookahead adder using structural Verilog supporting the following operations:

- addition

- subtraction

- logical AND

- set less than

- shift left logical

- shift right arithmetic

- shift right logical

- flags: zero, equal, overflow

Hierarchical modular design included creating 8-bit multiplexer, carry-lookahead adder stages and hierarchical units, shifter, and additional operation/output flag circuitry as submodules. Wrote circuitry and comprehensive tesbench for edge-case validation in Vivado. Design synthesized on Xilinx FPGA and uploaded to Python GUI for verification.